在微处理器系统中,所有的存储器(或I/O接口)都以地址来相互区分,根据访问存储器(或访问I/O接口)指令中的地址信息,其地址译码电路产生相应的地址选中信号,以选中所需的存储器(或I/O接口)。以存储器的接口为例,对于一般的8位微处理器,其存储器的地址线为16条(A0~A15),寻址范围为64K,但在一个实际系统中不一定扩展64K存贮器,而且所扩展的存贮器也不是一片容量为64K的存储器,因而整个系统通常要求扩展几片存贮器电路。每种存储器芯片都根据其容量需要一定的地址信号,如2K存储器所需的地址信号为A0~A10,8K存储器所需的地址信号为A0~A12。因此系统在连接存储器时除了向存贮器芯片提供必须的地址信号外,还应提供片选信号,使其中的一个芯片在片选信号有效时工作。地址译码电路就是提供片选信号的电路。例如一个系统需要连接2片2K存贮器,因此系统必须向存储器提供A10~A0的地址信号,以选中 2K存贮器中的某一个单元。为了区别这两个存储器芯片中那一个被选中,应另加片选信号,此信号由译码电路产生。

I/O接口所需的地址译码电路的原理与存储器相似,不同的是,通常I/O接口只需一个地址,或几个地址,而不象存储器一个芯片就占用较多的地址。因此对于I/O接口的译码电路,必须根据该设备占用的地址的数量来具体考虑。

地址译码通常采用全译码电路、部分译码电路、线选电路等不同的方式。

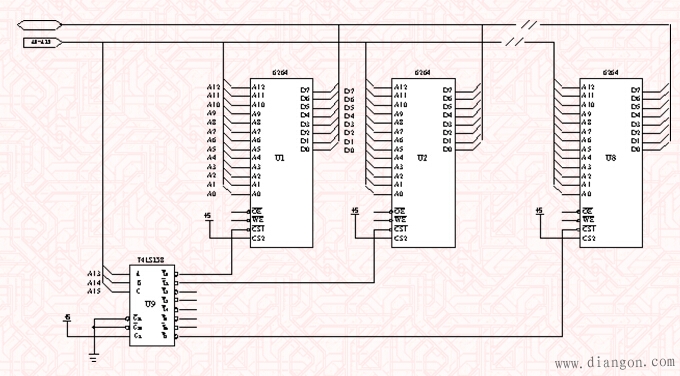

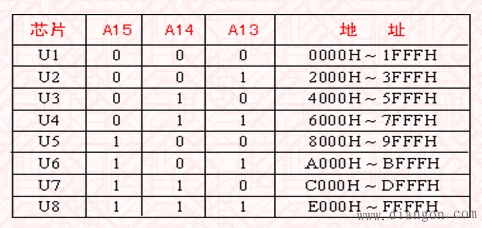

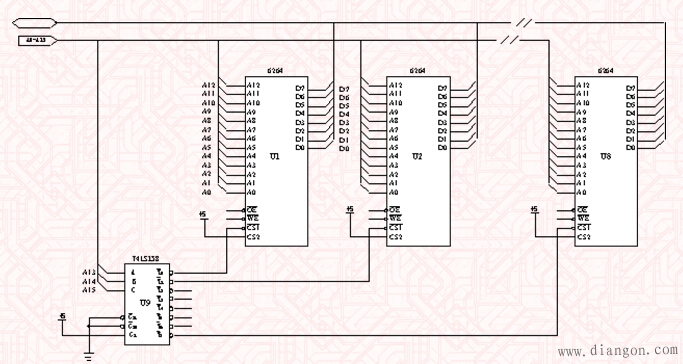

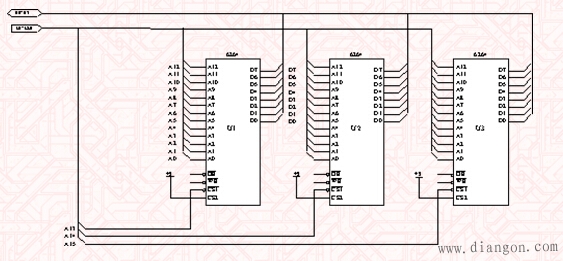

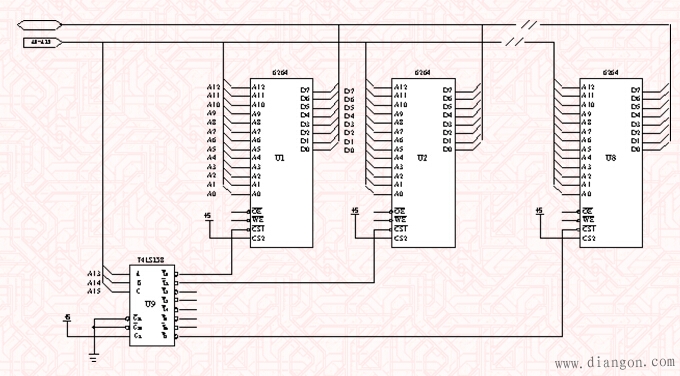

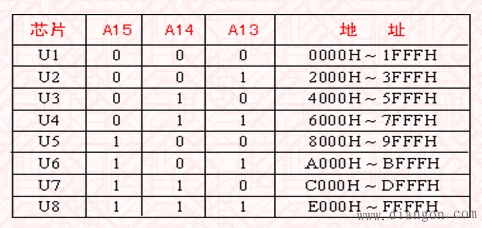

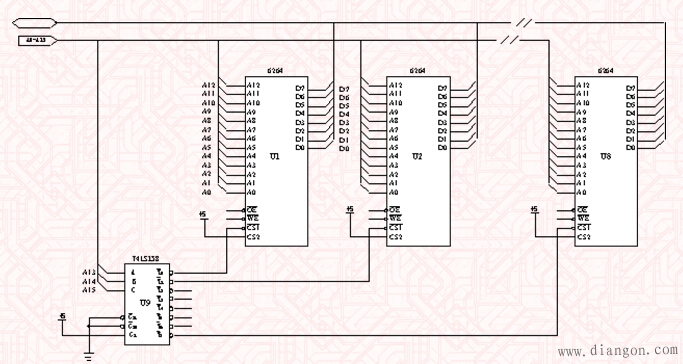

在系统中,存储器或I/O接口需使用部分地址信号,这些信号通常为地址信号中的低位地址信号,全译码电路将其余所有的高位地址信号经译码后作片选信号。在全译码电路的系统中,所有地址信号不是送入存储器或I/O接口芯片,就是送入了译码电路。译码电路的输出,即选中信号将与唯一的存储器或I/O接口的地址对应。如某个八位微处理器采用了I/O接口单独编址的方式,其选择存储器的地址线为16条(A0~A15),选择I/O接口的地址线为8条(A0~A7),则采用全译码电路时,选择存储器的地址译码电路必须包含A0~A15的地址信号中被存储器芯片所用的地址之外的所有地址信号,而选择I/O接口的地址译码电路必须包含A0~A7的地址信号中被I/O接口所用的地址之外的所有地址信号。图1为常用的译码电路74LS138、74LS13。根据存储器的容量,存储器所需的地址信号不同,因而在采用不同存储器时全译码电路的输入地址信号不同,图2为采用8K存储器的全译码电路,送入译码电路的地址信号为A13~A15。其地址分配表如表1所示。从地址分配表中可以看出,采用全译码方法时各存贮器芯片之间的地址是连续的,而且能最有效地利用 64K存贮空间。

(a) 74LS138 (b) 74LS139

图1 译码器的逻辑符号

图2 全译码电路扩展8K的存储器

表1 扩展8K存储器的地址分配

当系统需扩展的存储器或I/O接口的数量较少时,可采用部分译码电路。与全译码电路不同的是部分译码电路将存储器或I/O接口所用的低位地址线外的高位地址线中的部分地址信号作为译码电路的输入信号。采用这种方法的优点是减少了译码电路的输入信号,但译码的输出与地址不是一一对应的关系。由于未参加译码的地址信号可以有不同的编码,因而译码的输出可选中不同的地址。图3为采用2K存储器的部分译码电路,存储器所用的地址为A0~A10,如用全译码电路,输入到译码器的信号为A11~A15,而在图3中仅用了A11~A13,A14、A15未参加译码。这样A15、A14实际上可以存在4种情况,即00、01、10、11,以第一个芯片为例,当我们将A15、A14理解为00时,可在指令中以地址0000H~07FFH选中该芯片,但如果在指令中分别用了地址4000H~47FFH、8000H~87FFH、C000H~C7FFH选中的仍是该芯片,即一个单元可用几个地址来访问。

图3 部分译码电路

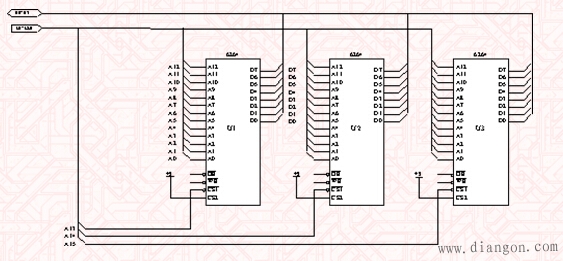

当系统需扩展的存储器或I/O接口的数量较少时,还可采用线选电路。以存储器的扩展为例,如系统扩展的为8K的存储器芯片,则地址信号A0~A12为存储器所使用,在全译码电路中,用地址信号A12~A15作为地址译码,而在如图4所示的线选电路中,这些信号将直接作为片选信号使用。很明显,能使用的地址线只有3条,因而最多只允许连接3片8K的存贮器,共24K的存储器容量。使用这种方法不能充分利用64K的存贮空间,常用于较小的系统。

图4 线选法译码电路

表2为利用线选的方法扩展3片存储器时地址的分配情况,从表中可以看出,尽管这种方法比较简单,但其使用的地址是不连续的,而且在使用时必须防止两条地址线同时为低电平,否则将使系统同时选中两个存储器芯片而无法正常工作。

表 2 线选电路存储器的地址分配

-

标签:

芯片 | A15 | A14 | A13 | 地 址 |

U3 | 1 | 1 | 0 | C000H ~ DFFFH |

U4 | 1 | 0 | 1 | A000H ~ BFFFH |

U5 | 0 | 1 | 1 | 6000H ~ 7FFFH |