一、结构与工作原理<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

1.结构

MOSFET的类型很多,按导电沟道可分为P沟道和N沟道;根据栅极电压与导电沟道出现的关系可分为耗尽型和增强型。功率场效应晶体管一般为N沟道增强型。从结构上看,功率场效应晶体管与小功率的MOS管有比较大的差别。小功率MOS管的导电沟道平行于芯片表面,是横向导电器件。而P-MOSFET常采用垂直导电结构,称VMOSFET(Vertical MOSFET),这种结构可提高MOSFET器件的耐电压、耐电流的能力。图1给出了具有垂直导电双扩散MOS结构的VD-MOSFET(Vertical Double-diffused MOSFET)单元的结构图及电路符号。一个MOSFET器件实际上是由许多小单元并联组成。

a) 结构图 b) 符号(N沟道) c) 符号(P沟道)

图1 MOSFET的结构图及电路符号

2.工作原理

如图1所示,MOSFET的三个极分别为栅极G、漏极D和源极S。当漏极接正电源,源极接负电源,栅源极间的电压为零时,P基区与N区之间的PN结反偏,漏源极之间无电流通过。如在栅源极间加一正电压UGS,则栅极上的正电压将其下面的P基区中的空穴推开,而将电子吸引到栅极下的P基区的表面,当UGS大于开启电压UT时,栅极下P基区表面的电子浓度将超过空穴浓度,从而使P型半导体反型成N型半导体,成为反型层,由反型层构成的N沟道使PN结消失,漏极和源极间开始导电。UGS数值越大,P-MOSFET导电能力越强,ID也就越大。

二、工作特性

1.静态特性

(1)漏极伏安特性

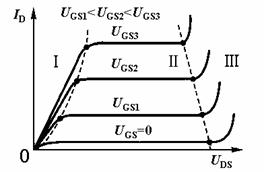

漏极伏安特性也称输出特性,如图2所示,可以分为三个区:可调电阻区Ⅰ,饱和区Ⅱ,击穿区Ⅲ。在Ⅰ区内,固定栅极电压UGS,漏源电压UDS从零上升过程中,漏极电流iD首先线性增长,接近饱和区时,iD变化减缓,而后开始进入饱和。达到饱和区Ⅱ后,此后虽UDS增大,但iD维持恒定。从这个区域中的曲线可以看出,在同样的漏源电压UDS下,UGS越高,因而漏极电流iD也大。当UDS过大时,元件会出现击穿现象,进入击穿区Ⅲ。

(2)、转移特性

漏极电流ID与栅源极电压UGS反映了输入电压和输出电流的关系,称为转移特性,如图3所示。当ID较大时,该特性基本上为线性。曲线的斜率gm=△ID/△UGS称为跨导,表示P-MOSFET栅源电压对漏极电流的控制能力,与GTR的电流增益β含义相似。图中所示的UGS(th)为开启电压,只有UGS>UGS(th)时才会出现导电沟道,产生栅极电流ID。

图2 漏极伏安特性 图3 转移特性

2.开关特性

P-MOSFET是多数载流子器件,不存在少数载流子特有的存贮效应,因此开关时间很短,典型值为20ns,而影响开关速度的主要是器件极间电容。图4为元件极间电容的等效电路,从中可以求得器件输入电容为Cin=CGS+CGD。正是Cin在开关过程中需要进行充、放电,影响了开关速度。同时也可看出,静态时虽栅极电流很小,驱动功率小,但动态时由于电容充放电电流有一定强度,故动态驱动仍需一定的栅极功率。开关频率越高,栅极驱动功率也越大。

P-MOSFET的开关过程如图5所示,其中UP为驱动电源信号,UGS为栅极电压,iD为漏极电流。当UP信号到来时,输入电容Cin有一充电过程,使栅极电压UGS只能按指数规律上升。P-MOSFET的开通时间为ton=td(on)+tr。当UP信号下降为零后,栅极输入电容Cin上贮存的电荷将通过信号源进行放电,使栅极电压UGS按指数下降,到UP结束后的td(off)时刻,iD电流才开始减小,故td(off)称为关断延迟时间。P-MOSFET的关断时间应为toff=td(off)+tf。

图4 输入电容等效电路 图5 开关特性

三、主要参数与安全工作区

1.主要参数

(1)漏极电压UDS

漏极电压UDS为P-MOSFET的电压定额。

(2) 电流定额ID

电流定额ID为漏极直流电流,IDM为漏极脉冲电流幅值。

(3) 栅源电压UGS

栅源间加的电压不能大于此电压,否则将击穿元件。

2.安全工作区

P-MOSFET是多数载流子工作的器件,元件的通态电阻具有正的温度系数,即温度升高通态电阻增大,使漏极电流能随温度升高而下降,因而不存在电流集中和二次击穿的限制,有较宽的安全工作区。P-MOSFET的正向偏置安全工作区由四条边界包围框成,如图6所示。其中Ⅰ为漏源通态电阻限制线;Ⅱ为最大漏极电流IDM限制线;Ⅲ为最大功耗限制线;Ⅳ为最大漏源电压限制线。

图6 P-MOSFET正向偏置安全工作区

全站搜索