复位RxFIFO:接收FIFO复位。当该位置位时,UART0接收FIFO中的所有字节被清零并复位指针逻辑。

注意:该位会自动清零。

复位TxFIFO:发送FIFO复位。当该位置位时,UART0发送FIFO中的所有字节被清零并复位指针逻辑。

注意:该位会自动清零。

―:这些位保留,用户程序不要向这些位写入1。

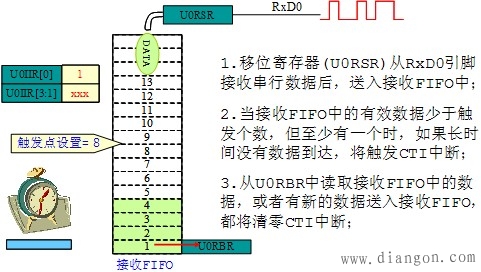

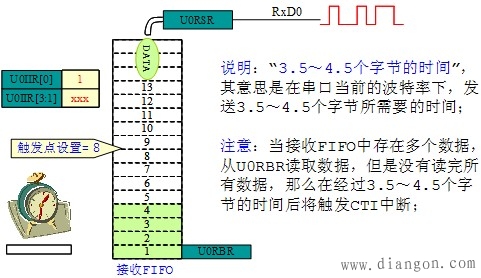

Rx触发点设置:通过设置这两位可以调整接收FIFO中触发RDA中断的有效字节数量。

00:触发点0(1字节); 01:触发点1(4字节);

10:触发点2(8字节); 11:触发点3(14字节);

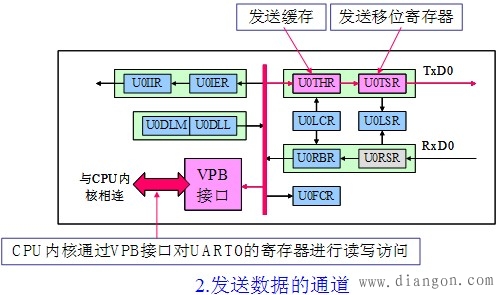

UART0相关寄存器描述

――线状态控制寄存器

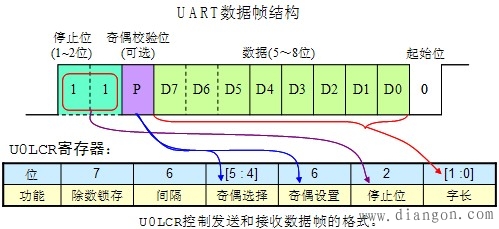

停止位:控制每帧数据包含的停止位个数。

0:1个停止位; 1:2个停止位;

奇偶使能:控制是否进行奇偶校验。如果使能,发送时将添加一位校验位。

0:禁止奇偶产生和校验; 1:使能奇偶产生和校验;

奇偶选择:设置奇偶校验类型。

00:奇数(数据位+校验位=奇数);

01:偶数(数据位+校验位=偶数);

10:校验位强制为1; 11:校验位强制为0;

间隔:当该位为1时,输出引脚(TxD0)强制为逻辑0,可以引起通信对方(LPC2000)产生间隔中断。在某些通信方式中,使用间隔中断作为通信的起始信号(如:LIN Bus)。

0:禁止间隔发送; 1:使能间隔发送;

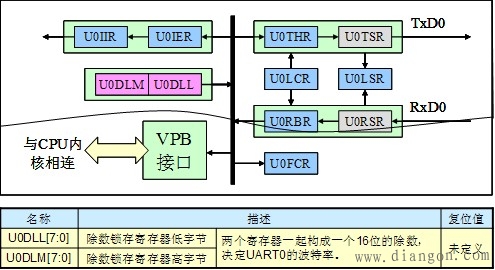

除数锁存:因为U0DLL和U0RBR/U0THR的地址重叠,通过设置该位可以指定其中某个寄存器操作。

0:禁止访问除数锁存寄存器; 1:使能访问除数锁存寄存器;

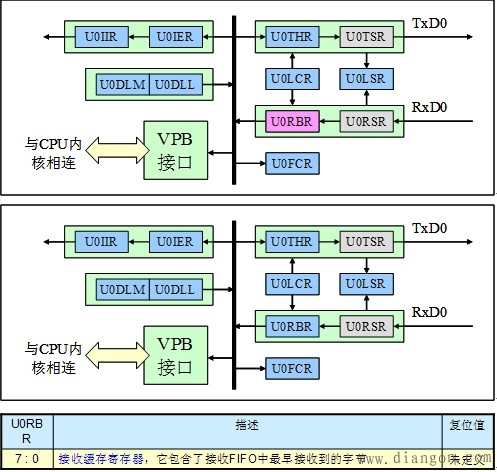

RDR:接收数据就绪。判断该位是否置一,决定能否从FIFO中读取数据。

0:U0RBR为空;

1:U0RBR中包含有效数据。从接收FIFO中读走所有数据后,恢复为0。

OE:溢出错误标志。当U0RBR寄存器中已经有新的字符就绪,而接收FIFO已满时,该位置位。

0:接收缓存区没有溢出;

1:接收缓存区发生溢出错误。

PE:奇偶校验错误。在使能奇偶校验位之后,对所有接收的数据都进行奇偶校验,如果与U0LCR中的设置不符,将引起奇偶校验错误。

0:没有发生奇偶校验错误;

1:发生奇偶校验错误。读操作使该位恢复为0。

FE:帧错误标志。当接收字符的停止位为0时,产生帧错误。

0:没有发生帧错误;

1:发生帧错误。读取该位时恢复为0。

BI:间隔中断标志。在发送数据时,如果RXD0引脚保持低电平,将产生间隔中断。发生间隔中断后,接收模块停止数据接收。

0:没有发生间隔中断;

1:发生间隔中断。

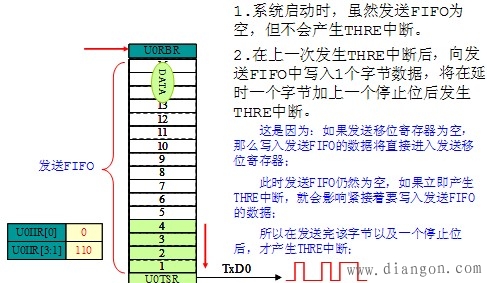

THRE:反映U0THR是否为空,也可以认为发送FIFO是否为空。

0:不为空;

1:空。对U0THR进行写操作,使该位恢复为0。

TEMT:当发送移位寄存器和U0THR均为空时,该位置位。

0:不为空;

1:空。对U0THR进行写操作,使该位恢复为0。

RXFE:如果一个带有接收错误(如帧错误、奇偶错误或间隔中断)的字符装入U0RBR时,该位置位。

0:U0RBR中没有接收错误,或U0FCR[0]为0;

1:U0RBR中包含至少一个UART0 Rx错误。

使用UART0注意要点

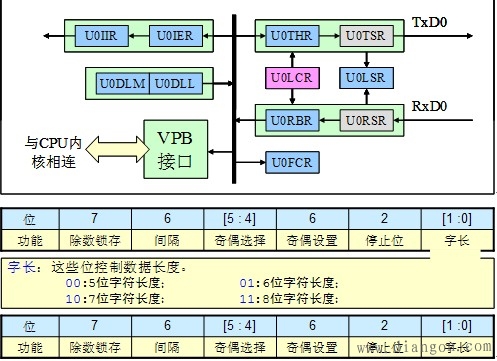

U0RBR与U0THR在同一地址上,但实际上是两个独立的寄存器,读操作时选择U0RBR,写操作时选择U0THR;

U0DLL与U0RBR/U0THR、U0DLM与U0IER在同一地址上,通过除数访问位DLAB选择。当该位为1时,选择U0DLL和U0DLM。为0时,选择U0RBR/U0THR和U0IER;

无论在U0FCR中是否使能FIFO,接收FIFO不能被禁止。关闭FIFO后,接收FIFO只有一个字节缓冲;

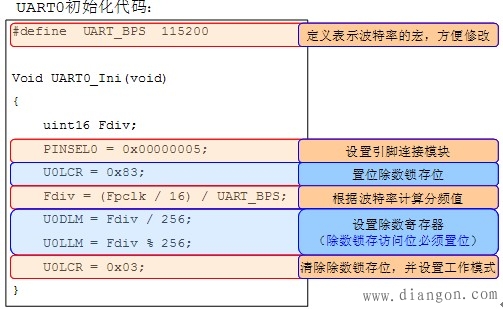

波特率计算公式:U0DLM、U0DLL = FPCLK/(16×baud);

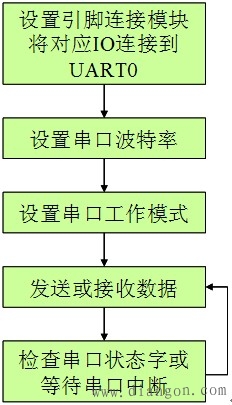

UART0应用示例――操作流程

全站搜索