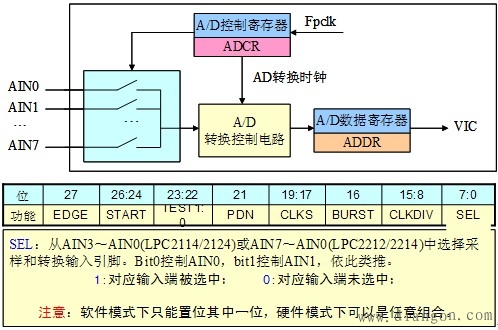

CLKDIV:将VPB时钟(PCLK)进行分频,得到AD转换时钟。分频后的时钟必须小于或等于4.5MHz。通常将CLKDIV编程为允许的最小值,以获得4.5MHz或稍低于4.5MHz的时钟。

A/D转换器时钟 = PCLK / ( CLKDIV + 1)

BURST:BURST/软件方式控制。当该位为0时,选择软件方式启动AD转换,需要11个时钟才能完成。当该位为1时,选择BURST(突发)模式启动AD转换,所需时钟数由CLK字段控制。

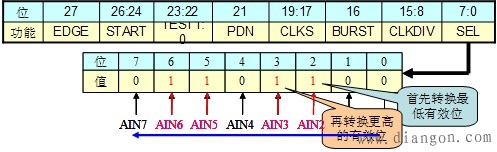

BURST模式下,对所有在SEL字段中置1的位对应的输入端进行转换,首先转换的是最低有效位。然后是更高的位。如此周而复始,直至该位清零。

CLKS:控制BURST模式下每次转换需要使用的时钟数和所得ADDR转换结果的LS位中可确保精度的位的数目,CLKS可在11个时钟(10位)~4个时钟(3位)之间选择:000=11个时钟/10位,001=10个时钟/9位,…111=4个时钟/3位。

PDN:控制AD部件是否工作。

1:A/D转换器处于正常工作模式; 0:A/D转换器处于掉电模式;

TEST1:0:器件测试控制位。

00:正常模式;01:数字测试模式;

10:DAC测试模式; 11:一次转换测试模式;

START:该字段用于控制AD转换的启动方式,该字段只有在BURST为0时有效。

000:不启动; 001:立即启动转换;

010:P0.16引脚出现预置的电平时,启动AD转换。以下值也具有相同特性;

011:P0.22引脚; 100:MAT0.1引脚; 101:MAT0.3引脚;110:MAT1.0引脚; 111:MAT1.1引脚;

EDGE:当START字段的值为010~111时,该位的设置有效。

0:在所选CAP/MAT信号的下降沿启动转换

1:在所选CAP/MAT信号的上升沿启动转换

A/D转换器寄存器描述

――数据寄存器

全站搜索